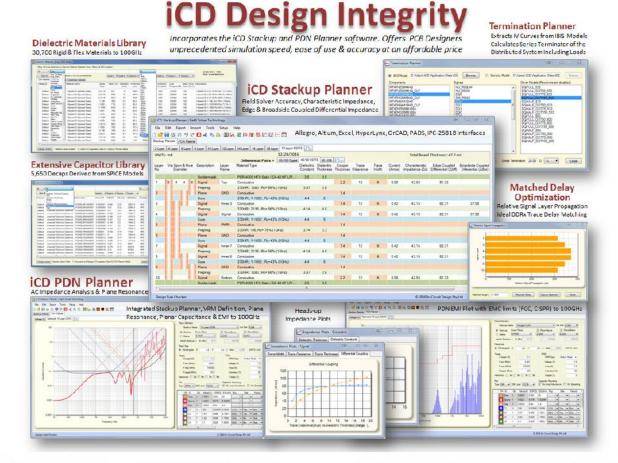

# iCD Stackup Planner - Offers Engineers & PCB Designers unprecedented simulation speed, ease of use and accuracy at an affordable price

- Industry Leading 2D (BEM) Field Solver precision

- Characteristic impedance, edge-coupled & broadside-coupled differentiall impedance

- Relative Signal Propagation with 'Matched Delay Optimization'-ideal for DDRx design

- Termination Planner series termination based on IBIS models & distributed system

- Unique Field Solver computation of multiple differential technologies per signal layer

- Extensive Dielectric Materials Library –over 30,700 rigid & flexible materials up to 100GHz

- Interfaces—Allegro, Altium, Excel, HyperLynx, OrCAD, PADS, Zmetrix TDR, Zuken & PC-2581B

# iCD PDN Planner - Analyze multiple power supplies to maintain low AC impedance over entire frequency range dramatically improving product performance

- Fast AC impedance analysis with plane resonance and projected EMI

- Definition of plane size, dielectric constant & plane separation

- Extraction of plane data from the integrated iCD Stackup Planner

- Definition of voltage regulator, bypass/decoupling capacitors, mounting loop inductance

- PDN EMI Plot with FCC, CISPR & VCCI Limits. Frequency range up to 100GHz

- Extensive Capacitor Library –over 5,650 capacitors derived from SPICE models

"iCD Design Integrity software features a myriad of functionality specifically developed for high-speed design." - Barry Olney

## **Transmission Line Losses**

### by Barry Olney

IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

As digital systems evolve and demand for new technology pushes the envelope for smaller and faster systems, transmission line losses, previously considered to be negligible, are becoming a primary design concern. Pragmatic effects such as frequency-dependent losses come into play at clock frequencies above 1 GHz and are of particular concern for fast rise time signals, with long trace lengths, such as multigigabit serial links. This frequency dependence causes rise time degradation and reduces the upper bandwidth of the signal resulting in reduced channel data transfer. In this month's column, I will look at the impact of transmission line losses on signal integrity.

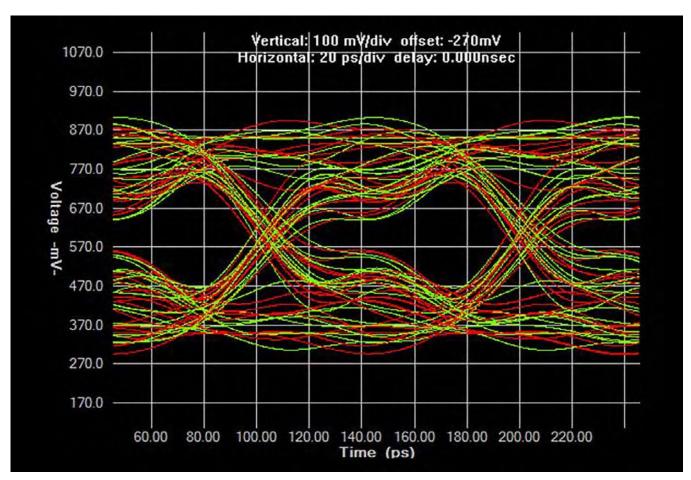

In an ideal world, where transmission line losses are independent of frequency, the entire signal waveform would uniformly decrease in amplitude, over distance, and the rise time would remain constant. This reduction in amplitude could easily be compensated for by applying gain (cranking up the volume) at the receiver. However, in practice, as signals propagate along a lossy transmission line, the amplitude of the high-frequency components is reduced, in magnitude, whereas the low-frequency components are unaffected. This selective attenuation, of high-frequency components, is the root cause of intersymbol interference (ISI) and collapse of the signal eye as in Figure 1.

Figure 1: Lossy transmission line with collapsing eye (simulated in HyperLynx).

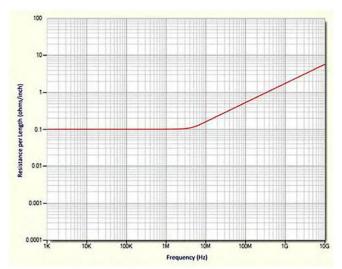

Figure 2: Resistance vs. frequency (5 mil, 1 oz, 50 ohm trace).

The capacitive and inductive properties of the transmission line do not, in themselves, absorb the high-frequency components of the signal but rather, the energy is reflected back to the source creating ringing and overshoot unless absorbed by a source termination.

To quantify the RF losses of a transmission line, one needs to consider the attenuation of each mechanism that can be broken down into at least four major components that are accumulated: metal loss, dielectric loss, conductivity of the dielectric and stray radiation.

The flow of charge through a material causes energy dissipation. The loss in both microstrip (outer layer) and stripline (inner layer) conductors may be broken down into two components: DC and AC losses. DC, in this context, is anything below 1 MHz. Although DC losses are not generally applicable to high-speed design, resistive drops can encroach on logic threshold levels and noise margins of multi-drop systems

such as long DDR3/4 address, command and control bus routing associated with SODIMM memory modules. However, on-board memory has typically less than three inches of signal length, and as such does not exhibit this issue.

For a typical 5 mil-wide trace, of 1.4 mil thickness (1oz Cu), one inch in length, the resistance, in the signal path at DC, is typically 0.1 ohm/inch. The bulk resistivity of copper-and most other metals-is constant with frequency until frequencies near 100 GHz. However, it is the skin effect that imposes a frequency dependency on conductors as shown in Figure 2.

AC—frequency-dependent—conductor losses can be resistive or inductive. At low frequencies, the resistance and inductance assume DC values, but as the frequency increases, the cross-sectional current distribution, in the transmission line and reference plane(s), becomes non-uniform and moves to the exterior of the conductor. The current is forced into the outer surface of the copper, due to the skin effect, dramatically increasing loss. This redistribution of current causes the resistance to increase and the loop inductance per length to decrease. As frequency increases beyond 1GHz, the resistance continues to increase while the loop inductance reaches a limiting value—the external inductance. The higher the frequency, the greater the tendency for current to flow in the outer surface of the conductor. The AC resistance will remain approximately equal to the DC resistance until the frequency increases to a point where the skin depth is smaller than the conductor thickness.

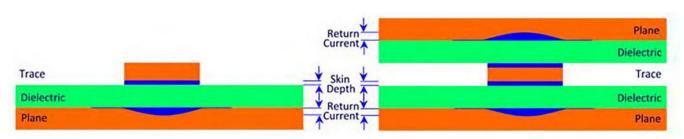

In a microstrip structure (Figure 3, left) the current (blue) will flow under the trace closest to the reference plane and only use the copper to the skin depth of the applicable frequency. However, in a stripline structure (right), the current will flow on both the top and bottom of

Figure 3: Skin depth of microstrip (left) and stripline (right) traces.

the trace and the proportion will depend on the proximity, of the trace, to the upper and lower reference planes that will share the return current. Essentially, routing in symmetric stripline structure doubles the current carrying capacity, of conductors, at high-frequencies.

There are two frequency-dependent processes that attenuate signals in a transmission line: the series resistance through the signal and return path conductors, and the shunt resistance through the lossy dielectric material.

Dielectric losses can also be broken down into two components: DC and AC losses. Since dielectric materials, used to fabricate PCBs, are not perfect insulators, there is a small DC loss associated with the DC drop across the material, between a signal conductor and reference plane(s). The direct current that flows in the capacitor, formed by the structure, is referred to as leakage current. However, the conductor losses are dominant and the DC loss is usually negligible. But as frequency increases, the AC loss also increases. Subsequently, it is important to understand the fundamental mechanisms that cause the dielectric losses to vary with frequency.

AC dielectric loss is the dissipation of energy, through the movement of charges, in an alternating electromagnetic field as polarization switches direction. When a voltage is applied across a capacitor, an electric field is generated.

This field will cause the dipoles, in the dielectric, to align with the field. The motion of these dipoles, alternating from one electrode to the other, appears as a transient current through the material. At high frequency, the conductivity increases due to the increased motion of the dipoles. The measure of the number of dipoles, in a material, and how far each can rotate, in the applied field, is called the dissipation factor (Df) or loss tangent  $(\delta)$  of the material.

Another important property of dielectric materials is the dielectric constant (Dk) or relative permittivity (Er). Dk is the ratio of the amount of energy stored in a material by an applied voltage, relative to that stored in a vacuum. If a material with a high dielectric constant is placed in an electric field, the magnitude of that field will be measurably reduced within the volume of the dielectric. Therefore, a lower Er is desirable for high-frequency design. Also, dielectric loss tends to be lower in materials with lower dielectric constants—which is also beneficial.

With so many materials to choose from, which are the best for your specific application? There are a number of factors to be considered:

- Low cost generally means low quality.

- The price of poor yield drives up the final material cost.

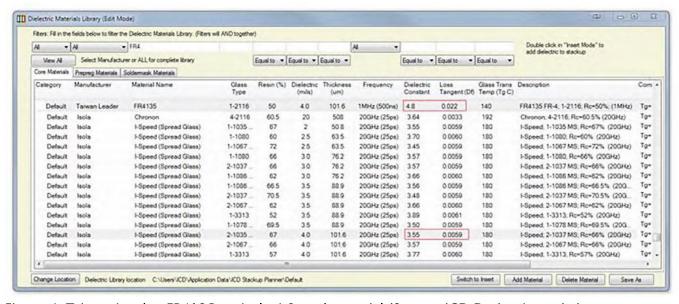

Figure 4: Taiwan Leader, FR4135 vs. Isola, I-Speed material (Source: iCD Design Integrity).

- Different materials are available locally compared to offshore.

- Materials are cheap in mass production compared to prototypes.

As an example, a low-cost FR-4 material such as Taiwan Leader FR4135 core has a Dk of 4.8 and Df of 0.022 specified at 1 MHz. On the other hand, a high-speed, 20 GHz material, Isola I-Speed (spread glass weave) material has a Dk of 3.55 and a Df of only 0.0059. Spread weave glass also helps eliminate skew and has far less loss than the standard FR-4 material. Selection of the most appropriate dielectric material is in important consideration for product performance. Figure 4, shows the properties of both materials in the iCD Dielectric Materials Library of over 31,000 rigid and flexible materials to 100 GHz.

Finally, while radiation loss is important, when it comes to electromagnetic compliancy (EMC), in practice the amount of energy lost to radiation is very small compared to other loss processes, and this mechanism will have little impact on the received signal.

As frequencies increase, engineers and PCB designers not only have to contend with technical challenges such as system timing, coupling, impedance discontinuities and radiation, but must also deal with a significant number of frequency dependent variables. However, choosing the right stackup and the most appropriate dielectric material, for your application, are a good start to reliable performance by increasing bandwidth and improving signal and power integrity.

### **Points to Remember**

- The frequency dependence of transmission lines causes rise time degradation and reduces the upper bandwidth of the signal resulting in reduced channel data transfer rate.

- As signals propagate along a lossy transmission line, the amplitude of the high-frequency components is reduced, in magnitude, whereas the low-frequency components are unaffected.

- High-frequency components are reflected back to the source, creating ringing and overshoot unless absorbed by a source termination.

- The skin effect imposes a frequency de-

pendency on conductors.

- As the frequency increases, the current is forced into the outer surface of the copper, due to the skin effect, dramatically increasing loss.

- The AC resistance will remain approximately equal to the DC resistance until the frequency increases to a point where the skin depth is smaller than the conductor thickness.

- Routing in symmetric stripline structure essentially doubles the current carrying capacity, of conductors, at high-frequencies.

- AC dielectric loss is the dissipation of energy, through the movement of charges, in an alternating electromagnetic field as polarization switches direction. At high frequency, the conductivity increases due to the increased motion of the dipoles.

- A low Dk is desirable for high-frequency design. Also, dielectric loss tends to be lower in materials with lower dielectric constants-which is also beneficial.

- Selection of the most appropriate dielectric material is in important consideration for product performance.

- The amount of energy lost to radiation is very small compared to other loss processes. **PCBDESIGN**

#### References

- 1. Barry Olney's Beyond Design columns: Transmission Lines-from Barbed Wire to High-Speed Interconnects, Material Selection for SERDES Design.

- 2. Transmission Line Losses—Microwaves 101.

- 3. Signal and Signal Integrity Simplified, by Eric Bogatin.

- 4. High-Speed Digital System Design, by Stephen Hall.

Barry Olney is managing director of In-Circuit Design Pty Ltd (iCD), Australia. The company is a PCB design service bureau specializing in board-level simulation, and developed the iCD Design Integrity software incorporating the iCD

Stackup, PDN and CPW Planner. The software can be downloaded from www.icd.com.au.