# The Impact of PDN Impedance on EMI

#### **Beyond Design**

Feature Column by Barry Olney, IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

In last month's column, I looked at why interconnect impedance is so important to the performance of our system. I also mentioned that impedance is defined in both the time and the frequency domains. In the time domain, we need to consider the impact of the interconnect impedance on the propagation of electromagnetic energy. However, in the frequency domain, the AC impedance needs to be kept below an acceptable level to prevent excessive radiation.

Decoupling capacitors are generally spread throughout the power distribution network (PDN). In the past, we thought that it was only necessary to add a few capacitors to each IC power pin to stabilize the power at that device. That worked fine at low frequencies. Thinking in the time domain, you can say that decoupling capacitors store and supply charge to the loads until the power supply can respond. However, in the frequency domain, decoupling capacitors also lower the impedance at different frequencies to help meet the AC impedance target. Thus, there are two distinct functions of capacitors that work in unison but in different domains. In this month's column, I will look at impedance in the frequency domain and its impact on EMI.

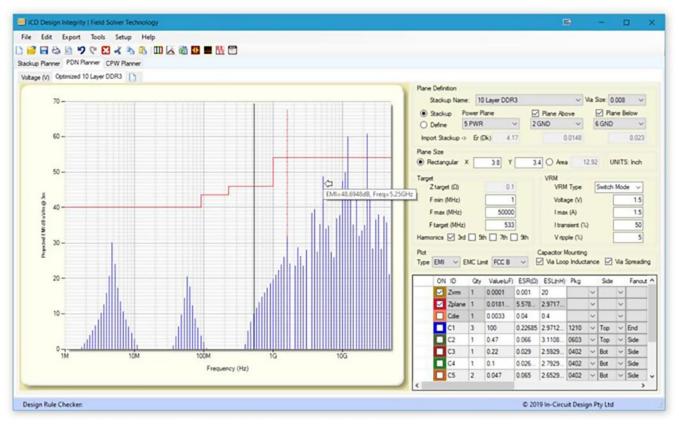

The PDN acts like an on-board ecosystem (Figure 1). If one small part of the PDN were to change, then the entire network performance may be impacted. This is particularly noticeable when mounting, loop, and spreading inductance are added to the profile of the capacitors. Inductance has its greatest influence in the high-frequency band, where odd harmon-

Figure 1: The PDN acts like an on-board ecosystem.

Figure 2: Odd harmonics of the fundamental tend to radiate at high frequencies (iCD PDN Planner).

ics of the fundamental tend to radiate if impedance peaks appear at the harmonics (Figure 2). Inductance pushes the impedance up and shifts the resonant frequency of capacitors down. The addition of more capacitors to the PDN lowers the impedance at particular frequencies, while the combined parallel resistance determines the minimum impedance at the resonant frequency (dips).

The PDN has four major functions:

- 1. Provides a low-impedance, high-current supply path to the ICs.

- 2. Reduces noise on the power supply at the IC die.

- 3. Minimizes ground bounce and common-mode potential between the IC die and the return path.

- 4. Reduces electromagnetic radiation from the board fringing fields.

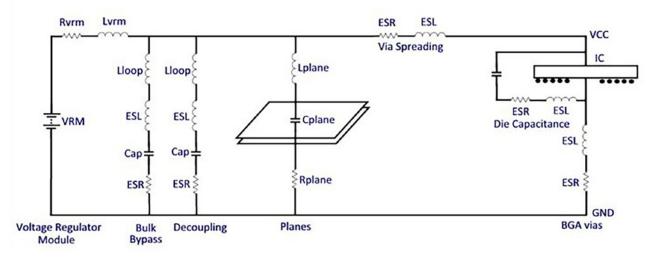

The typical PDN topology (Figure 3) consists of numerous connections from the voltage regulator module (VRM) to the capacitors, vias, wide traces, copper pours, power and ground planes, solder balls, and interconnects on the IC silicon itself. The PDN must provide a constant supply voltage within a tolerance of 5% at the power pins of each IC. This voltage must be stable from DC up to the maximum bandwidth, which is typically five times the fundament frequency. At the same time, these connections that provide the power are also tasked with providing the return signal path. This is where high-current, simultaneous switching noise from the power supply can interfere with the signal return currents.

When the return current flows through the impedance of a cavity between two planes, it generates voltage. Although quite small, the accumulated noise from simultaneous switching devices can become significant. Unfortunately, as core voltages drop, noise margins become tighter. This voltage, emanating from the vicinity of the signal via, injects a propagating wave into the cavity, which can excite the cavity resonances or any other parallel structure (e.g., between copper pours over planes). Other signal vias passing through

Figure 3: Typical PDN topology.

this cavity can pick up this transient voltage as crosstalk.

The more switching signals that pass through the cavity, the more noise is induced into other signals; it affects vias all over the cavity, not just the ones in close proximity to the aggressor signal vias. This cavity noise propagates as standing waves spreading across the entire plane pair. This is the primary mechanism by which highfrequency noise is injected into cavities: by signals transitioning through cavities, using each plane successively as the signal return path.

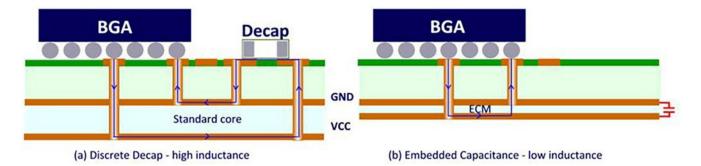

If the plane cavity is not dampened, then electromagnetic fields can radiate from the board (as in Figure 2). However, when optimized, the PDN can mitigate many potential EMI issues and help prevent EMC certification test failures. How do we effectively dampen the plane cavity? With the continuous trends to smaller feature sizes and faster signal speeds, planar capacitor laminate, and embedded capacitor materials (ECM) are becoming a cost-effective solution for improved power integrity. This technology provides an effective approach for decoupling high-performance ICs whilst also reducing electromagnetic emissions.

Embedded capacitance technology has a very thin dielectric material (0.24–2.0 mils) sandwiched between two copper planes that produce distributive decoupling capacitance and takes the place of conventional discrete decoupling capacitors over 1 GHz (Figure 4). Unfortunately, standard decoupling capacitors have little effect over 1 GHz, and the only way to reduce the impedance of the PDN above this frequency is to use ECM or alternatively on-die capacitance. These ultra-thin laminates replace the conventional power and ground planes and should be positioned in the stackup close to and directly below/above the IC. This reduces the loop inductance dramatically. With a capacitance density of up to 20 nF per square

| Manufacturer          | Material       | Description                                | Thickness (mils)       |

|-----------------------|----------------|--------------------------------------------|------------------------|

| 3M                    | ECM            | Embedded capacitance materials             | 0.24, 0.47, 0.55       |

| DuPont                | Interra HK4,11 | Ultra-thin laminate                        | 0.5, 1.0               |

| Integral Technology   | Zeta Bond      | High-Tg, epoxy-based adhesive film         | 1.0, 1.5, 2.0          |

| Integral Technology   | Zeta Lam SE    | Low-CTE, C-stage dielectric with a high Tg | 1.0                    |

| Integral Technology   | Zeta Cap       | High-performance polymer-coated copper     | 1.0                    |

| Oak-Matsui Technology | FaradFlex      | Planar capacitor                           | 0.31, 0.47, 0.63, 0.94 |

| Samina                | ZBC-1000       | Buried capacitance, high-performance       | 1.0                    |

| Samina                | ZBC-2000       | decoupling                                 |                        |

|                       |                | Buried capacitance, high-performance       | 2.0                    |

|                       |                | decoupling                                 |                        |

Table 1: ECM (available in the iCD Dielectric Materials Library).

inch and extremely low inductance, 3M ECM is the highest capacitance density material on the market. Table 1 lists available ECMs. ECMs have excellent stability of dielectric constant (Dk) and dissipation loss (Df) up to 15 GHz.

These specialized ECMs are precision-fabricated laminates with extremely thin dielectrics. However, if your budget is limited, then a planar capacitor can be constructed with two build-up layers so that they are close to the top/bottom of the stackup. Alternatively, use a thin 2-mil laminate as a plane pair on the inner layers. These are not as good as ECM but much better than a typical thicker laminate. Please check the minimum thickness with your fabrication shop first.

The goal of designing a high-performance PDN is to reduce the impedance peaks below the target impedance level and push the peak frequency components above the bandwidth of the signals.

To achieve this, one needs to reduce cavity resonance and emissions.

• A thin dielectric in the plane cavity is the most effective way of reducing the peak amplitude of the modal resonance. It reduces spreading inductance and the impedance of the cavity and reduces the resonance peaks by damping the high-frequency components. Thinner plane separation implies less area of equivalent magnetic current at the plane pair edge, or equivalently less local fringing field volume, and therefore lower emissions for a given field strength

- A dielectric material with a high Dk should be selected to add more planar capacitance. This is contrary to the typical choice of high-speed materials that require a low Dk. Remember, we are talking about the dielectric embedded between the planes, which have little impact on the signal properties

- The parallel resonant frequencies of the cavity can be pushed up above the maximum bandwidth of the signals by reducing the plane size and by adding stitching vias between (similar) planes of a cavity

- Where the length of a rectangular plane is a simple multiple of its width—such as 1, 1.5, or 2—the resonant frequencies of the length and width directions will coincide at some frequencies, causing higher-Q peaks (more intense resonances) than usual. Thus, it is best to avoid square planes and simple L:W ratios by choosing irrational numbers

- When plane pairs resonate, their emissions come from the fringing fields at the board edges. With ground/power plane pairs, edge-fired emissions can be reduced by reducing the plane separation, as described earlier, but this technique cannot generally be used for multiple planes. Alternatively, make the power planes slightly smaller (~200 mils) than the GND plane. This modifies the pattern of the fringing fields, pulling them back from the edge, and may help reduce emissions to some extent

Planar capacitance can reduce EMI by minimizing the loop area, power supply ripple, and plane resonance. It is also up to three times better at heat transfer compared to a standard core. System price performance can also be improved by reducing the discrete capacitor count and the size of the PCB and by improving signal and power integrity. The best feature is that it is truly a drop-in replacement for standard core materials. If you need a quick fix for the PDN, look no further!

#### **Key Points**

- In the time domain, decoupling capacitors store and supply charge on demand to the loads

- In the frequency domain, decoupling capacitors also lower the impedance at different frequencies to help meet the AC impedance target

- Inductance pushes the AC impedance up and shifts the resonant frequency of capacitors down

- High-current simultaneous switching noise from the power supply can interfere with the signal return currents

- As core voltages drop, noise margins become tighter

- The voltage, emanating from the vicinity of the signal via, injects a propagating wave into the cavity, which can excite the cavity resonances or any other parallel structure

- This cavity noise propagates as standing waves spreading across the entire plane pair

- If the plane cavity is not dampened, then electromagnetic fields can radiate from the board

- When optimized, the PDN can mitigate many potential EMI issues and help prevent EMC certification test failures

- Planar capacitor laminate or ECM is becoming a cost-effective solution for improved power integrity

- ECM takes the place of conventional discrete decoupling capacitors over 1 GHz

- These ultra-thin laminates replace the conventional power and ground planes

and should be positioned in the stackup close to IC

• ECMs can have a capacitance density of up to 20 nF per square inch and extremely low inductance **DESIGN007**

#### **Further Reading**

B. Olney, "Beyond Design: Plane Crazy, Part 1," *The PCB Design Magazine*, December 2015.

B. Olney, "Beyond Design: Plane Crazy, Part 2," *The PCB Design Magazine,* January 2015.

B. Olney, "Beyond Design: PDN Planning and Capacitor Selection, Part 1," *The PCB Design Magazine*, December 2013.

B. Olney, "Beyond Design: PDN Planning and Capacitor Selection, Part 2," *The PCB Design Magazine*, January 2014.

B. Olney, "Beyond Design: Decoupling Capacitor Placement," *The PCB Design Magazine,* January 2016.

B. Olney, "Beyond Design: Plane Cavity Resonance," *The PCB Design Magazine*, September 2017.

B. Olney, "Beyond Design: Ground Bounce," *Design007 Magazine*, January 2018.

B. Olney, "Beyond Design: The 10 Fundamental Rules of HSD, Part 3," *Design007 Magazine,* November 2018.

B. Olney, "Beyond Design: Materials Selection for SERDES Design," *The PCB Design Magazine*, September 2013.

Oak-Mitsui Technologies, "Improved Power Delivery and Reduce Noise with Embedded Capacitance."

I. Novak, Signal Integrity Journal.

E. Bogatin, *Signal and Power Integrity: Simplified,* Prentice Hall, 2008.

**Barry Olney** is managing director of In-Circuit Design Pty Ltd. (iCD), Australia, a PCB design service bureau that specializes in boardlevel simulation. The company developed the iCD Design Integrity software incorporating the iCD

Stackup, PDN, and CPW Planner. The software can be downloaded at icd.com.au. To read past columns or contact Olney, click here.

## We **DREAM** Impedance!

Did you know that two seemingly unrelated concepts are the foundation of a product's performance and reliability?

- Transmission line impedance and

- Power Distribution Network impedance

etwork impedance

iCD software quickly and accurately analyzes impedance so you can sleep at night.

### iCD Design Integrity: Intuitive software for high-speed PCB design.

"iCD Design Integrity software features a myriad of functionality specifically developed for PCB designers." — Barry Olney

**DISCOVER MORE**

www.icd.com.au